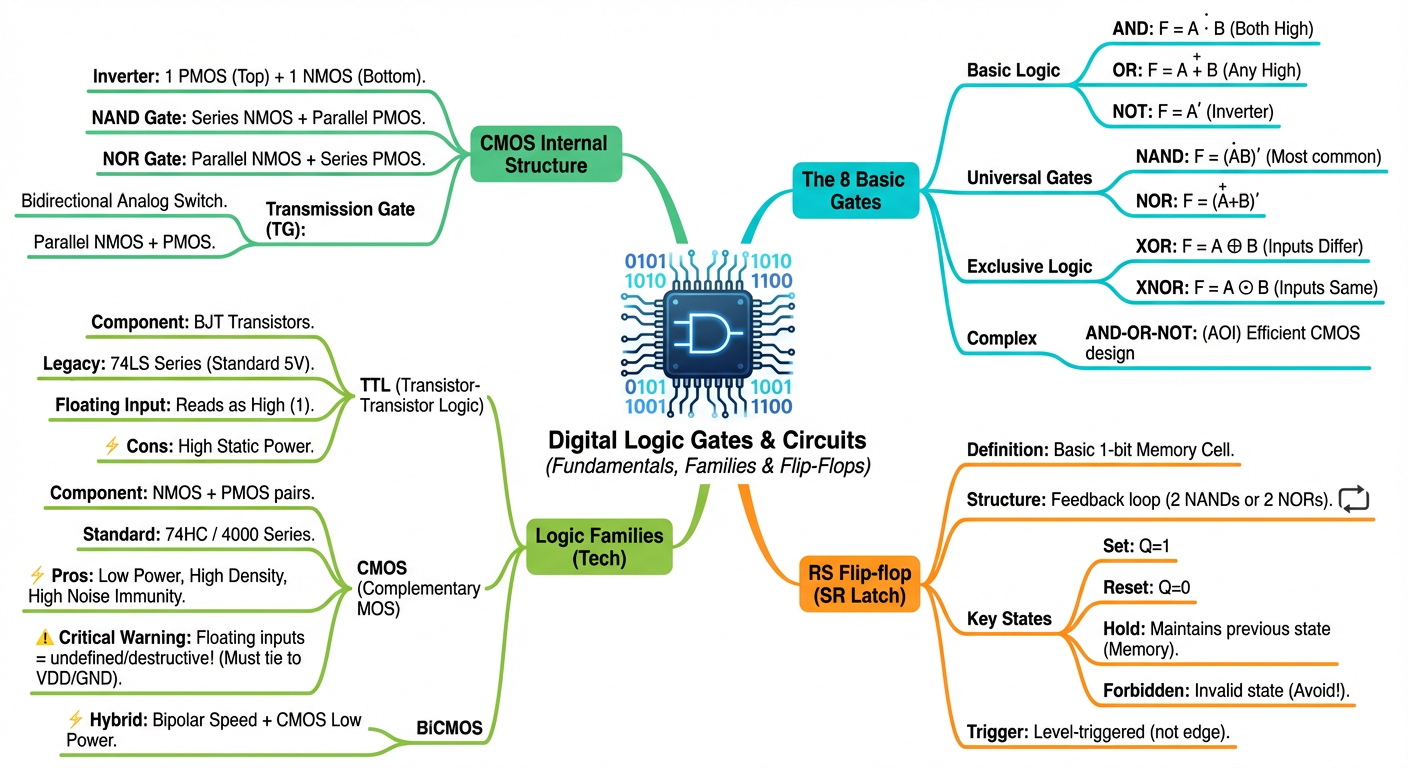

Introduction to TTL and CMOS Logic Gate Circuits

How Logic Gates Work - The Learning Circuit

Catalog

I What is a Logic Gate?

Electronic circuits that implement basic logic operations are called logic gate circuits. The gate implementing the AND operation is the AND gate, the one implementing the OR operation is the OR gate, and the one implementing the NOT operation is the NOT gate (also called the inverter).

In standard Positive Logic systems: Logic 1 represents a high voltage level (e.g., 5V or 3.3V), and Logic 0 represents a low voltage level (Ground or 0V).

1. AND Gate

Logical expression: F = A · B

The output Y is 1 only when input terminals A and B are both 1. Otherwise, Y is 0. Classic TTL chip models of AND gates include the 74LS08 and 74LS09 (open collector).

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 0 | 0 | 0 | 1 |

AND Truth Table

2. OR Gate

Logical expression: F = A + B

When at least one of the input terminals (A or B) is 1, the output terminal Y is 1. Y will be 0 only when both inputs are 0. Common chip models include the 74LS32.

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 0 | 1 | 1 | 1 |

OR Truth Table

3. NOT Gate (Inverter)

Logical expression: F = A' (or F = A)

The output is always the inverse (complement) of the input. If Input is 1, Output is 0, and vice versa. Common chip models include 74LS04 and 74LS14 (Schmidt Trigger).

| A | 0 | 1 |

| F | 1 | 0 |

NOT Truth Table

4. NAND Gate

Logical expression: F = (A · B)'

The output Y is 0 only when all inputs are 1. If any input is 0, the output is 1. NAND is known as a Universal Gate because any other logic gate can be constructed using only NAND gates. Common models: 74LS00.

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 1 | 1 | 1 | 0 |

NAND Truth Table

5. NOR Gate

Logical expression: F = (A + B)'

The output Y is 1 only when all inputs are 0. If any input is 1, the output is 0. Like the NAND gate, the NOR gate is also a Universal Gate. Common models: 74LS02.

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 1 | 0 | 0 | 0 |

NOR Truth Table

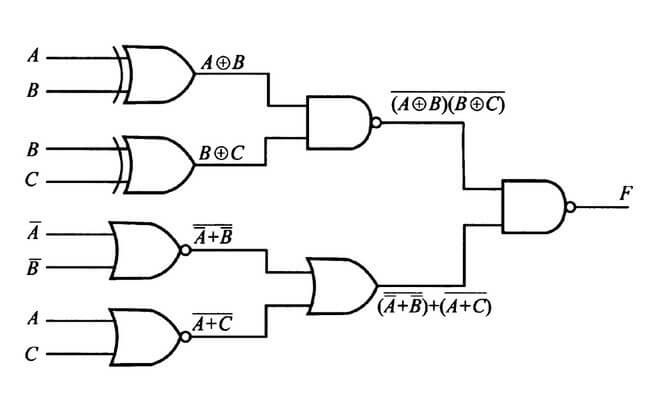

6. XNOR Gate (Exclusive-NOR)

Logical expression: F = A⊙B = AB + A'B'

Also known as the "Equivalence Gate." The output is 1 if both inputs are the same (both 0 or both 1). If inputs differ, the output is 0.

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 1 | 0 | 0 | 1 |

XNOR Truth Table

7. XOR Gate (Exclusive-OR)

Logical expression: F = A⊕B = A'B + AB'

The output is 1 if the inputs are different. If inputs are the same, the output is 0. This is widely used in arithmetic circuits (adders).

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| F | 0 | 1 | 1 | 0 |

XOR Truth Table

8. AND-OR-NOT Gate (AOI Logic)

Logical expression: F = (A · B + C · D)'

Often called an AND-OR-Invert (AOI) gate. It consists of two AND gates driving a NOR gate. This structure is very efficient in CMOS transistor design compared to stacking independent gates.

| A | 0 | 0 | ... | 1 |

| B | 0 | 0 | ... | 1 |

| C | 0 | 0 | ... | 1 |

| D | 0 | 1 | ... | 1 |

| F | 1 | 1 | ... | 0 |

AND-OR-NOT Truth Table

II RS Flip-flop (SR Latch)

1. Circuit Structure

The basic RS flip-flop (often called an SR Latch) can be constructed using two NAND gates or two NOR gates. The image below shows the NAND gate version. It has two input terminals R (Reset) and S (Set), and two output terminals Q and Q'.

Note: In a NAND-based SR latch, the inputs are Active Low. This means the latch is triggered by logic 0 (Low level).

Figure 1. Basic RS flip-flop Circuits Diagrams (NAND Latch)

The logic equation of the basic RS flip-flop is derived from the cross-coupled feedback loop:

Based on the NAND configuration, the relationship between inputs and outputs is:

(1) Set State: When S=0 and R=1, the output Q=1 (and Q'=0). The flip-flop is "set" to 1.

(2) Reset State: When S=1 and R=0, the output Q=0 (and Q'=1). The flip-flop is "reset" to 0.

Since the inputs are active low, the schematic symbols for the S and R pins often feature small circles (bubbles) to indicate this negation.

(3) Hold State (Memory): When both inputs are inactive (S=1, R=1), the flip-flop maintains its previous state. This is the "memory" function of the circuit.

(4) Forbidden State: When both R=0 and S=0 at the same time, both NAND outputs would try to go High (1). This is logically invalid because Q and Q' must be complements. Furthermore, if both inputs return to 1 simultaneously, the final state is unpredictable (indeterminate). This condition must be avoided in design.

Figure 2. Basic RS flip-flop Consists of 2 NOR Gates (Active High Inputs)

2. Characteristic Equation

3. Features

It serves as the basic memory cell (1-bit storage).

Inputs are level-sensitive (not edge-triggered).

It is susceptible to interference; noise on the input lines can inadvertently flip the state.

Requires input constraints (R and S cannot be active simultaneously) to avoid the indeterminate state.

III TTL Logic Gate Circuits

TTL (Transistor-Transistor Logic) circuits use Bipolar Junction Transistors (BJTs) as the primary switching element. The classic 7400 series (specifically the 74LS Low-power Schottky series) was the industry standard for decades.

Characteristics of TTL:

Standard Voltage: 5V supply.

Speed: Relatively fast switching.

Power: Higher static power consumption compared to modern CMOS.

Input Behavior: A "floating" (unconnected) TTL input reads as a Logic 1 (High), though good practice dictates tying unused inputs to VCC or Ground.

IV CMOS Logic Gate Circuits

1. TTL VS. CMOS

CMOS (Complementary Metal-Oxide-Semiconductor) has largely replaced TTL as the dominant technology for digital integrated circuits, from simple logic gates (like the 74HC and CD4000 series) to complex CPUs.

Advantages of CMOS:

Low Power: Extremely low static power consumption. Current flows primarily only during switching.

High Density: Transistors are smaller, allowing millions (or billions) to fit on a chip.

Noise Immunity: Better noise margins than TTL.

Warning: Unlike TTL, a floating CMOS input is undefined and can oscillate or cause the transistor pair to conduct simultaneously, leading to overheating and destruction. Unused CMOS inputs must always be tied to VDD or Ground.

2. CMOS Inverter

The CMOS inverter is the fundamental building block. It uses one PMOS transistor (top) and one NMOS transistor (bottom).

Logic Operation:

Input Low (0V): The PMOS is ON, and the NMOS is OFF. The output connects to VDD (High).

Input High (VDD): The NMOS is ON, and the PMOS is OFF. The output connects to Ground (Low).

In both stable states, one transistor is always off, resulting in negligible current flow (high input impedance and low static power).

Figure 2. Current flow when Input = VDD (Output Low)

Figure 3. Current flow when Input = 0V (Output High)

Transmission Characteristics

The switch-over point typically occurs at VDD/2. During the brief transition from 0 to 1, both transistors act partly as resistors, causing a momentary spike in current (dynamic power consumption).

Working Speed

Speed is determined by how fast the transistors can charge and discharge the load capacitance (CL). While early CMOS was slower than TTL, modern sub-micron CMOS processes are incredibly fast, with switching times in picoseconds for processor cores, though discrete logic (like 74HC) still operates in the nanosecond range (approx 10ns propagation delay).

3. CMOS Logic Gate Circuit

(1) NAND Gate Circuit

A CMOS NAND gate uses Series NMOS (bottom) and Parallel PMOS (top).

If both Inputs are High, both NMOS conduct to Ground (Output Low).

If any Input is Low, that PMOS path conducts to VDD (Output High).

Figure 5. 2-input CMOS NAND Gate Logic Diagram

Function: ![]()

(2) NOR Gate Circuit

A CMOS NOR gate uses Parallel NMOS (bottom) and Series PMOS (top).

Figure 6. 2-input CMOS NOR Gate Circuit

Function:

Note: In general silicon fabrication, series-connected PMOS transistors (used in NOR gates) are slower and larger than series-connected NMOS transistors (used in NAND gates) due to the lower mobility of holes carriers. Therefore, NAND gates are generally preferred in CMOS library design over NOR gates.

(3) XOR Gate Circuit

Figure 7. CMOS XOR Gate Circuit

This implementation uses a combination of basic gates or transmission gates. The logical output is: ![]()

4. BiCMOS Gate Circuit

BiCMOS (Bipolar CMOS) technology combines the high input impedance and low power of CMOS with the high current-driving capability and speed of Bipolar (TTL) transistors.

It is particularly useful for driving I/O lines or high-capacitance loads where pure CMOS might be too slow. However, it involves a more complex fabrication process.

5. CMOS Transmission Gate (Analog Switch)

The Transmission Gate (TG) acts as a bidirectional relay controlled by logic. It consists of a PMOS and NMOS in parallel.

Figure 11. CMOS Transmission Gate Structure

When the Control signal (C) is High, the gate closes (conducts), allowing analog signals to pass in either direction. When C is Low, the gate opens (high impedance). The parallel arrangement ensures that the switch resistance remains relatively constant across the full voltage range of the input signal.

Summary

Understanding these 8 basic logic gates and the underlying technologies (TTL vs CMOS) is crucial for electronics design. While TTL defined the early era of digital logic, CMOS is the standard for modern high-density, low-power applications.

Latest Electronic Blogs:

1.What is TTL logic and CMOS logic?

The types of logic devices are classified in "families", of which the most important are TTL and CMOS. The main families are: TTL (Transistor-Transistor Logic), made of bipolar transistors. CMOS (Complementary Metal Oxide Semiconductor) made from MOSFETs. ECL (Emitter Coupled Logic) for extremely high speeds.

2.What is difference between CMOS and TTL?

TTL circuits utilize BJTs while CMOS circuits utilize FETs. 2. CMOS allows a much higher density of logic functions in a single chip compared to TTL. TTL circuits consumes more power compared to CMOS circuits at rest.

3.What is TTL in logic circuits?

Transistor–transistor logic (TTL) is a logic family built from bipolar junction transistors. TTL manufacturers offered a wide range of logic gates, flip-flops, counters, and other circuits. Variations of the original TTL circuit design offered higher speed or lower power dissipation to allow design optimization.

4.What is CMOS logic gate?

CMOS logic gates are made of IGFET (MOSFET) transistors rather than bipolar junction transistors. CMOS gate inputs are sensitive to static electricity. B-series CMOS gates have “buffered” outputs to increase voltage gain from input to output, resulting in faster output response to input signal changes.

5.What are the 7 logic gates?

There are seven basic logic gates: AND, OR, XOR, NOT, NAND, NOR, and XNOR. The AND gate is so named because, if 0 is called "false" and 1 is called "true," the gate acts in the same way as the logical "and" operator.

Introduction to TTL and CMOS Logic Gate CircuitsUTMEL24 November 202521090

Introduction to TTL and CMOS Logic Gate CircuitsUTMEL24 November 202521090Electronic circuits that implement basic and common logic operations are called logic gate circuits. TTL and CMOS logic gate circuits are 2 typical types. Read this to learn their structure and features.

Read More What is Sequential Logic?UTMEL15 October 20207532

What is Sequential Logic?UTMEL15 October 20207532Sequential logic is an important part of digital logic circuit, which is mainly composed of storage circuit and combinational logic circuit. Sequential logic is also called sequential logic circuit. It is different from other circuits that we are familiar with. Its output state at any time is determined by the input signal and the original state of the circuit at that time, and its state is mainly memorized and represented by the storage circuit.

Read More

Subscribe to Utmel !

Product

Product Brand

Brand Articles

Articles Tools

Tools